This post is based on a Gestalt IT Showcase by Intel Corporation

Intel recently announced that it is coming to market with a new series of Ethernet switches based on the Tofino 2 programmable chipset, the core technology of which came from the acquisition of Barefoot Networks in mid-2019.

Intel recently announced that it is coming to market with a new series of Ethernet switches based on the Tofino 2 programmable chipset, the core technology of which came from the acquisition of Barefoot Networks in mid-2019.

Standing on their own, the total throughput and programmability attributes of the Tofino 2 are impressive and open up a new range of use-cases for bandwidth-intensive environments like hyper-scale datacenters.

However, Intel is taking things a step further by co-packaging their Silicon Photonics technology in the place of traditional optical transceivers, increasing the amount of bandwidth that can be efficiently consumed per-port.

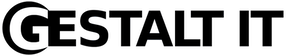

Although much of the conversation around the co-packaged Tofino 2 and Photonics switch seems focused on high-density scenarios, perhaps the most interesting potential use is to further enable disaggregation of resources and a transition away from the traditional all-encompassing x86 server node.

With that, an interesting question comes to mind – how does the development of this new switching platform impact the future of Intel’s Rack Scale Design and overall composable disaggregated strategy?

Escaping the Boundary of the x86 Server

The limitations of a single x86 server are well-known, and its fixed ratios of computing, storage, and networking capacity have been a constraint the technology industry has worked against for some time.

To escape this boundary and move certain types of resources outside of the individual server so they can be consumed and scaled independently, a very high speed and low latency external interconnect technology is needed.

Previous attempts to disaggregate resources have relied on technologies like PCI Express and Ethernet for this purpose. Of these two, Ethernet is far more prominent when used as an external interconnect is concerned, and it is becoming more widely used as a generic transport every year.

However, as Ethernet reaches the speeds (100Gb+) required to be competitive with PCI Express in attaching high-bandwidth external devices, the efficiency of traditional optical transceivers become a significant limitation.

This is where Silicon Photonics comes into play. Because transmitted data does not have to be converted back and forth between light and an electrical signal, more switch resources are available for achieving higher port density and per-port bandwidth levels.

To make resource disaggregation realistic, though, the switch ASIC itself has to be up to the task, as well. It just so happens that the Tofino 2, being one of the fastest Ethernet ASICs available, has enough aggregate bandwidth available to bring this all together.

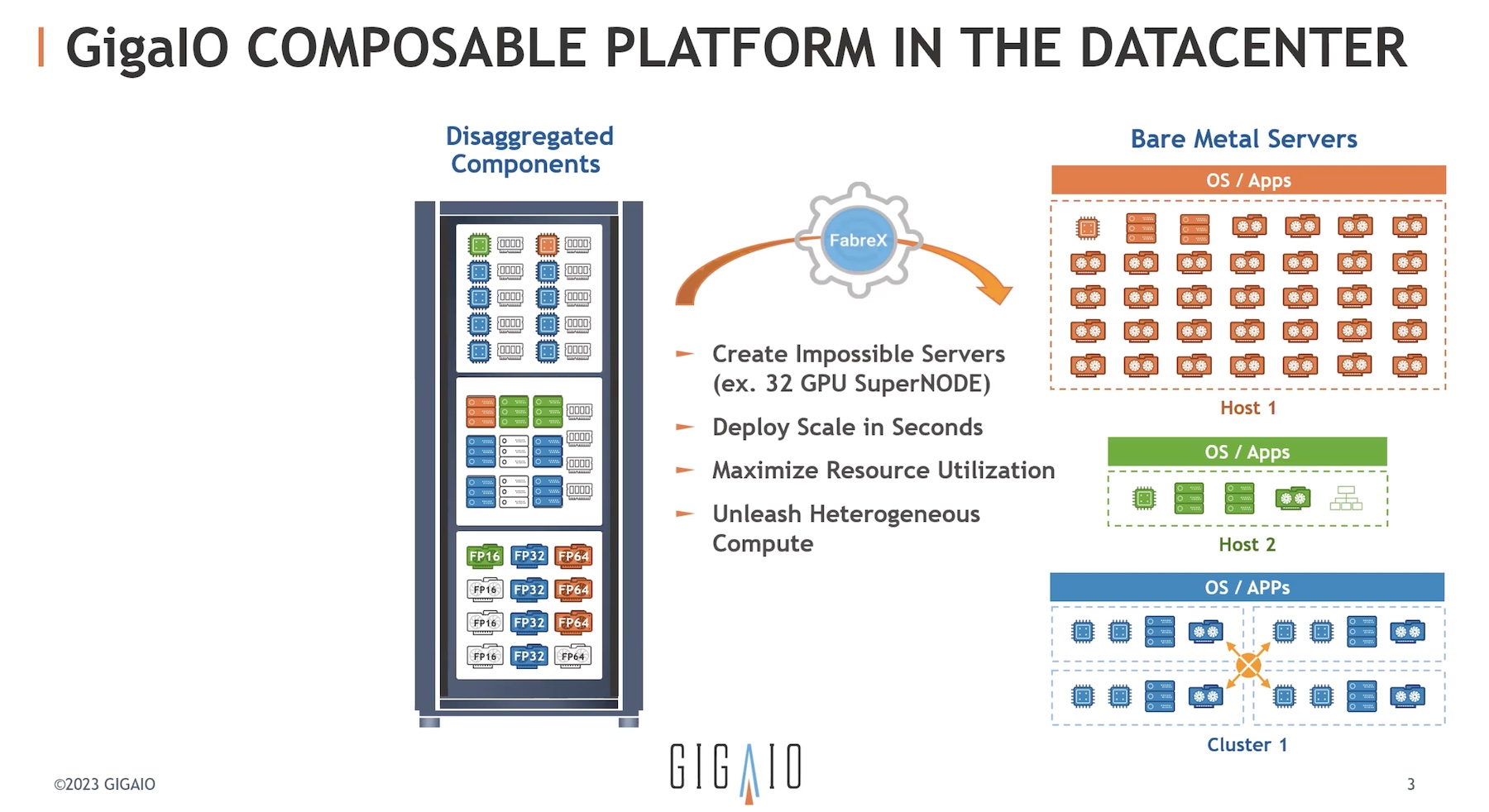

Considering these items, the situation has become very interesting for Intel. As a manufacturer of CPU’s, FPGA’s, GPU’s, SSD’s, storage-class memory, and (now) high-speed Ethernet switching, Intel now has all of the major components beneath one roof to push their vision of composable disaggregated infrastructure forward to the next iteration.

Conclusion

While Ethernet may or may not replace PCI Express as the transport of choice when connecting disaggregated resources like GPU’s and FPGA’s to the compute resources that consume them, it’s becoming a more realistic proposition at the per-port bandwidths that Silicon Photonics enables.

As we’ve seen generally with the popularity of composable systems that are already on the market, a growing number of customers appreciate the flexibility and economics that can come along with the pooling and as-needed allocation of hardware resources. The potential to use a ubiquitous and flexible interconnect like Ethernet for this purpose strengthens the value proposition further.

In any case, it will be very interesting to see what impact these technologies have on the future of disaggregated architectures, and the options they ultimately provide to customers. The strategic decisions being made lead one to believe that the usefulness of Tofino 2 with Photonics in this context is not just a fortunate accident.